LID World

Summit

June 23-25, 2026 | Grenoble, France

CEA-Leti’s

flagship event

Discover sustainable semiconductor breakthroughs to guide your roadmap from lab-to-market and to tomorrow’s AI factory at LID World Summit 2026.

Join industry leaders to discover groundbreaking innovation that will help meet technological goals for the healthcare, automotive, industrial, defense, and consumer-electronics sectors. Leave with confidence in the possible.

8:30

9:30

10:00

12:00

12:30

2:30

3:30

4:30

5:00

6:00

Tuesday June, 23

Welcome Coffee

Exhibitions & business meetings

throughout the day

Plenary Session

CxOs Talks

Lunch

Exhibitions & business meetings

throughout the day

Plenary Session

CxOs Talks

Coffee break

Exhibitions & business meetings

throughout the day

starting at 6:30 p.m.

Evening Reception

Elixir & Gastronomy

Registration is mandatory

Wednesday June, 24

Welcome Coffee

Exhibitions & business meetings

throughout the day

Lunch

Exhibitions & business meetings

throughout the day

Coffee break

Exhibitions & business meetings

throughout the day

starting at 6:45 p.m.

Evening Reception

Château de Sassenage

Registration is mandatory

Thursday June, 25

Welcome Coffee

Exhibitions & business meetings

throughout the day

Lunch

Exhibitions & business meetings

throughout the day

Closure of the exhibitions at 04:00 p.m.

Plenary Session

Disruptive Digital Interfaces

Plenary Session

Special Guest Closure

Tuesday June, 23

Doors open at 8:30 a.m.

Welcome Coffee

Exhibitions & business meetings

throughout the day

10:00 a.m. – 12:30 p.m.

Plenary Session

CxOs Talks

Lunch

Exhibitions & business meetings

throughout the day

2:30 p.m. – 5:00 p.m.

Plenary Session

CxOs Talks

Coffee break

Exhibitions & business meetings

throughout the day

starting at 6:30 p.m.

Evening Reception

Elixir & Gastronomy

Registration is mandatory

Wednesday June, 24

Doors open at 8:30 a.m.

Welcome Coffee

Exhibitions & business meetings

throughout the day

9:30 a.m. – 12:00 p.m.

Data and Network

—

Cloud Convergence

9:30 a.m. – 12:00 p.m.

Semiconductors

for Defense

9:30 a.m. – 12:00 p.m.

ChipsAct 1

The Fames

Pilot Line

Lunch

Exhibitions & business meetings

throughout the day

2:30 p.m. – 4:30 p.m.

Semiconductors

for Computing

2:30 p.m. – 4:30 p.m.

Cybersecurity

2:30 p.m. – 4:30 p.m.

ChipsAct 2

Resolve

Initiative

Coffee break

Exhibitions & business meetings

throughout the day

starting at 6:45 p.m.

Evening Reception

Château de Sassenage

Registration is mandatory

Thursday June, 25

Doors open at 8:30 a.m.

Welcome Coffee

Exhibitions & business meetings

throughout the day

9:30 a.m. – 12:00 p.m.

Optical

Interconnects

9:30 a.m. – 12:00 p.m.

Tech Talks:

Shaping What’s Next

9:30 a.m. – 12:00 p.m.

Startups

& Investments

Lunch

Exhibitions & business meetings

throughout the day

2:30 p.m. – 3:30 p.m.

Plenary Session

Disruptive Digital Interfaces

3:30 p.m. – 4:30 p.m.

Plenary Session

Special Guest Closure

Closure of the exhibitions at 04:00 p.m.

Designed to bring you

maximum value

High-level speakers

Latest technologies

Business meetings

Networking

represented

partners, and exhibitors

Meet some of the keynote speakers

Tim Breen

Chief Executive Officer, GF

Tim Breen

Chief Executive Officer, GF

Bio:

Tim Breen is Chief Executive Officer (CEO) of GF, a position he was appointed to in 2025, having joined the company in 2018.

Prior to becoming CEO, Mr. Breen served as GF’s Chief Operating Officer (COO), overseeing the company’s global operations, including the manufacturing, quality, supply chain and digital transformation teams. Earlier in his tenure at GF he held various executive roles including leading strategy, business transformation and finance. Prior to joining GF, Mr. Breen served as a member of the senior leadership team of GF’s founding shareholder, Mubadala Investment Company (Mubadala). Earlier in his career, he was a partner with McKinsey & Company in Abu Dhabi.

Mr. Breen holds a Master of Business Administration degree from London Business School and is based in New York.

Thomas Rueckes

Chief Executive Officer, FMC

Thomas Rueckes

Chief Executive Officer, FMC

Bio:

Thomas Rueckes is a senior semiconductor executive and inventor with deep expertise in advanced memory technologies, company building, and industrial-scale execution. He is currently CEO of Ferroelectric Memory Company (FMC), where he leads the development and commercialization of high-performance non-volatile memory products spanning NV-DRAM+ in Memory Fabs and high density Near Compute Memory, 3D-CACHE+ in advanced logic foundries. His work bridges materials, devices, integration, packaging, and system-level deployment, with active engagement across tier-1 memory IDMs, hyperscalers, OEMs, and leading equipment and materials suppliers.

Previously, Dr. Rueckes was Co-Founder, CTO, and COO of Nantero, where he spent more than two decades building one of the industry’s most advanced emerging memory platforms, overseeing R&D, operations, manufacturing scale-up, IP strategy, fundraising, government programs, and strategic partnerships. He holds more than 200 granted patents and has published extensively in leading scientific journals. Dr. Rueckes earned his Ph.D. in Nanotechnology from Harvard University, with earlier training in surface science at Imperial College London UK as well as chemistry and physics at Philipps University of Marburg, Germany. He is bilingual in English and German and brings extensive experience translating deep science into globally competitive semiconductor products and companies.

Audrey Charles

Senior Vice President of Corporate Strategy & Advanced Packaging; President of Lam Capital

Audrey Charles

Senior Vice President of Corporate Strategy & Advanced Packaging; President of Lam Capital

Bio:

Audrey Charles is senior vice president of corporate strategy and advanced packaging, and president of Lam Capital at Lam Research. In this position, she is responsible for leading the executive management team in the development of strategic priorities and key initiatives that support the company’s long-term profitable growth. She is also responsible for accelerating the company’s market-leading position in advanced packaging to deliver differentiated technology and support to customers.

Additionally, Audrey oversees Lam’s Corporate Development team and investment arm, Lam Capital, which invests in disruptive companies that advance the semiconductor ecosystem through next generation industrial automation, technology and product innovation, and new market opportunities. She brings a broad base of experience to her role, including engineering, customer technology management and investor relations. Since joining Lam in 1995, she has served in a range of leadership positions including senior vice president of Global Human Resources and vice president of corporate initiatives.

Audrey earned an M.B.A. from the MIT Sloan School of Management and a B.S. in applied physics from Dublin City University.

Takaki Murata

Senior Vice President & Executive Board Member, Murata

Takaki Murata

Senior Vice President & Executive Board Member, Murata

Bio:

Takaki Murata has been involved in technology development, accounting, planning, and business management at the Company and its group companies for many years and corporate management as a chief officer at business companies in the United States, accumulating a wealth of experience and a solid record of achievement. He has been elected as a Member of the Board of Directors because the Company expects that he will continue to strengthen the decision-making and supervisory functions of the Board of Directors.

Abstract:

The rapid scaling of AI and high‑performance computing workloads is driving a fundamental transformation of data center power architectures, from on‑package integrated voltage regulators to high‑voltage power supply units. In this context, passive components are no longer commodities but critical system enablers.

This presentation introduces Murata’s silicon capacitor technologies and roadmaps, highlighting how continuous innovations in three‑dimensional charge density, voltage capability, and reliability unlock new design spaces for advanced power delivery. Leveraging deep‑trench and nanoporous architectures, Murata silicon capacitors combine ultra‑low ESL/ESR, exceptional thermal and frequency stability, predictable aging, and high customization flexibility.

We will illustrate how these characteristics enable thin, high‑frequency integrated voltage regulator modules close to processors, as well as high‑voltage silicon capacitors for next‑generation data center power supplies operating up to 800V nominal.

Agnieszka Thonet

Senior Director of Technology, HP

Agnieszka Thonet

Senior Director of Technology, HP

Bio:

Agnieszka has over 23 years of digital transformation and product innovation experience. Recognized as a thought leader in emerging technologies and trends, she has a strong track record of managing and aligning global high performance multicultural teams to deliver strategic value.

Over the past 16 years she has held multiple technical and management roles across HP businesses. As Senior Engineering Director, she drove the delivery of full stack software on devices and to Enterprise customers. As Head of Innovation Partnerships, she gathered and led cross-industry, multidisciplinary research experts to create open collaboration models that unleashed impactful innovation. Her breadth of knowledge ranges from electronics and communication systems to digital manufacturing and complex cyber-physical architectures.

Fluent in four languages, she holds a MSc in Communication Systems Engineering from the University of the Basque Country in Spain.

Chih-I Wu

Vice President & Senior Expert, ITRI

Chih-I Wu

Vice President & Senior Expert, ITRI

Bio:

Dr. Chih-I Wu is the VP and Senior Expert at Industrial Technology Research Institute (ITRI), as well as a professor in Graduate Institute of Photonics and Optoelectronics and Department of Electrical Engineering of National Taiwan University. He was the General Director of Electronic and Optoelectronic System Research Laboratories, ITRI, from 2015 to 2022. His research is mainly on 2D material and devices, organic optoelectronics, metal-semiconductor interfaces, and heterojunctions. Prior to joining NTU, he worked at Component Research Lab of Intel in the US from 2000 to 2004. His work at Intel was mainly on developing the advanced VLSI process technology, such as Cu and low k interconnects, metal gate materials, and atomic layer deposition process. Dr. Wu got his B.S. degree from National Taiwan University and M.S. degree from Northwestern University, both in Physics. He received his Ph.D. from Princeton University in Electrical Engineering.

Abstract:

In the talk, I will share with you ITRI’s strategy on internation collaboration. I will start from the evolution of Taiwan’s semiconductor ecosystem, from 1970’s till now. The current status and the future of both Taiwan and global semiconductor industry will also be presented from our perspective. Based on the evolution and future prediction of semiconductor ecosystem, ITRI’s strategy on international collaboration will be discussed in this presentation.

Hajime Shoji

Executive Officer, General Manager of Transmission Devices Laboratory, Sumitomo Electric Industries

Hajime Shoji

Executive Officer, General Manager of Transmission Devices Laboratory, Sumitomo Electric Industries

Bio:

Hajime Shoji received the Ph.D. degree in electronic engineering from the University of Tokyo, and joined Fujitsu Laboratories in 1990. He moved to Eudyna Devices, a joint venture of Fujitsu and Sumitomo Electric in 2004, then after the change in organization, moved to Sumitomo Electric Industries, LTD. in 2009. He has been consistently leading the development of compound semiconductor materials and devices for optical and microwave communications. Currently, he is serving as a general manager of the Transmission Devices Laboratories, and also as an executive officer of Sumitomo Electric.

Abstract:

Optical device technologies play a fundamental role in combination with electronics toward photonics-electronics convergence. In the presentation, our development activities focusing on heterogeneous integration of III-V compound semiconductor and silicon and its application to advanced optical devices will be described. Photonics-electronics integration platform technologies will be also presented together with topics on some related devices.

Dr. Atsuyoshi Koike

Chief Executive Officer, Rapidus corporation

Dr. Atsuyoshi Koike

Chief Executive Officer, Rapidus corporation

Bio:

ATSUYOSHI KOIKE established Rapidus Corporation, a Japanese advanced logic semiconductor company in August 2022. Prior to this role, Koike had served as President of Western Digital Japan since April 2018. Prior to joining Western Digital, he held the position of president and chief executive officer at Trecenti Technologies, Inc., as well as served as corporate chief engineer for Renesas Technology Corporation. Prior to that, he held senior manufacturing management and executive leadership positions at Hitachi, Ltd. Koike received the B.S. and M.S. in Materials Science and Engineering from Waseda University and Ph.D. in Electronic Engineering from Tohoku University.

Bill Chang

Co-founder, President & CTO, Density AI

Bill Chang

Co-founder, President & CTO, Density AI

Bio:

Bill Chang is the Co-founder, President, and Chief Technology Officer of DensityAI, a company focused on making AI infrastructure radically more efficient and sustainably scalable, by building the world's densest AI compute platform, integrating innovations across technology, chip and system architecture, software, and datacenter infrastructure.

Prior to founding DensityAI, Chang served as Chief System Architect at Tesla, where he was responsible for the design and architecture of the Dojo supercomputer, a vertically integrated high-performance AI training system. He led the development of the first production wafer-scale package technology, enabling machine learning training to scale to exaFLOP levels.

Before Tesla, Chang was at Apple, where he managed the transition of the Mac platform to Apple Silicon. Earlier in his career, he held various technical leadership roles at IBM Microelectronics spanning DRAM, CMOS technology development, and manufacturing, building deep expertise in silicon design and semiconductor process engineering.

Sébastien Dauvé

Chief Executive Officer, CEA-Leti

Sébastien Dauvé

Chief Executive Officer, CEA-Leti

Bio:

Sébastien Dauvé was named CEO of CEA-Leti effective on July 1, 2021, after more than twenty years of experience in microelectronics technologies and their applications, including clean mobility, medicine of the future, cybersecurity, and power electronics.

Sébastien Dauvé started his career at the French Armament Electronics Center, where he worked on developing synthetic-aperture radar. In 2003, he joined CEA-Leti as an industrial transfer manager and supervised several joint research laboratories, in particular with the multinational Michelin.

In 2007, Sébastien Dauvé became a laboratory manager, then head of an R&D department in the area of sensors applied to the Internet of things and electric mobility. During this time, he supported the dissemination of new technologies in industry, including the automotive industry (Renault), aeronautics, national defense (SAFRAN), and microchips with the industry leader Intel. He played an active role in the creation of start-ups in application fields ranging from health to infrastructure security, leading to dozens of new jobs. In 2016, he became Director of the CEA-Leti Systems Division.

From sensors to wireless communication, Sébastien Dauvé has played an active role in the digital transformation, focused on coupling energy frugality and performance. He has made cross-disciplinary approaches central to innovation by harnessing the expertise of talented teams with diverse backgrounds. Their goal is to provide technological tools for meeting the major societal challenges of the future.

Sébastien Dauvé is a graduate of the French Ecole Polytechnique and the National Higher French Institute of Aeronautics and Space (ISAE-SUPAERO).

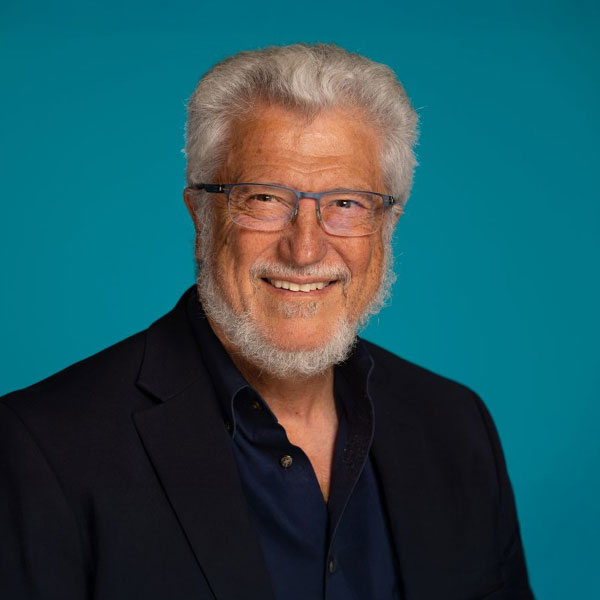

Elliott Mc Namara

SVP & Head of the 3D DUV, ASML

Sylvie Gellida

General Manager, Optical and RF Foundry Division, STMicroelectronics

Sylvie Gellida

General Manager, Optical and RF Foundry Division, STMicroelectronics

Bio:

Sylvie Gellida is STMicroelectronics’ General Manager, responsible for the Optical and RF Foundry Division, belonging to RF and Optical Communication product sub-group since January 2025.

Sylvie Gellida started her career as RF design engineer in Dolphin before joining ST Grenoble in 2000. In 2006, she joined the Foundry team as technical support and program manager, extended to marketing next, to sell ST differentiated RF silicon technologies. In 2021, she took the leadership of the mmW products Business Unit, as well as the RF technologies strategy position, encompassing the Silicon Photonics technology and business development from 2023. Since January 2025, Sylvie has been leading the Optical and RF Foundry Division, covering optical interconnects, LEO satellites communications and mmW markets.

Abstract:

Enabling energy-efficient data centers requires a fundamental shift from copper-based electrical links to high-bandwidth, low-loss optical connectivity. This talk will present ST’s silicon photonics strategy and the role of the PIC100 platform in replacing copper with integrated SiPho solutions for next-generation data center and AI interconnects. By combining differentiated Silicon Photonics, BiCMOS platforms in advanced packaging technologies, ST overcome the challenges of power efficient optical interconnects.

Jean-René Lèquepeys

Deputy Director and Chief Technology Officer, CEA-Leti

Jean-René Lèquepeys

Deputy Director and Chief Technology Officer, CEA-Leti

Bio:

Jean-René Lèquepeys received an engineering degree in 1983 from CentraleSupélec, a top French graduate engineering school at Paris-Saclay University, France. He taught physics during 2 years in Ouarzazate, Morocco.

He joined CEA, a French Research and Technology Office focusing on applied research, in Paris Saclay in 1985. He first worked at the laboratory of the Central Security Office, on the evaluation of means of detection and intrusion. Two years later, he was promoted head of this laboratory.

In 1993, he moved to Grenoble, France, and joined the System Division of CEA-Leti. He worked on different projects in the field of image processing and telecommunication technologies. In particular, he was responsible for the "Telecom, Communicating Objects and Smart Card" programs from 1999 to 2004.

In 2005, he took the responsibility of the Circuits Design Division at CEA-Leti (200 people). He launched new research activities at CEA such as a new laboratory in Aix-en-Provence, France, on the development of secured chips. In 2000, Jean-René Lèquepeys received the prestigious award from the french Société de l'Electricité, de l'Electronique et des technologies de l'information et de la communication (SEE) "Grand Prix de l'électronique Général Ferrié" for his work in the telecommunications field (he holds 15 patents).

In 2010, he launched a new division at CEA focusing on Electronic Architectures, Integrated Circuit Design and Embedded Software. He established the structure on two sites (Paris and Grenoble) and led the division twice in his career.

He rapidly got involved in the creation of the Silicon Components Division at CEA-Leti, and took the lead of it in 2011 managing 350 people. Division encompasses micro and nanoelectronics (SOI, nanodots, quantum, memories, 3D technologies, substrates), Micro Systems (sensor, actuator, radiofrequency components) and Power Components. He established the French Nano2022 Program for research funding in microelectronics.

In 2019, he was appointed Chief Technology Officer of CEA-Leti, overseeing Science, relations with the European Commission, Industrial Partnership and Strategic Program Management in the scope of the institute (2,000 people, ~€350m budget). He took the responsibility of the Microelectronic Program at CEA level, spearheading technological and upstream research in the field of semiconductor technologies. For the past 2 years, he has been strongly involved in the CEA-Leti Next Gen FD-SOI project in the frame of France2030 and has played a key role in European chips Act pilot line promoting FD-SOI and Gate All Around technologies.

Having dedicated his career to applied research, he is regularly invited as a keynote speaker in international semiconductor conferences.

Jean-René is also Vice President of ACSIEL, a professional trade union gathering industrial companies in the French electronic value chain, member of the Board of EPOSS, the European Technology Platform on Smart Systems Integration, a member of the Board of AENEAS, the Association for Europoean NanoElectronics Activities, and an expert consultant for the European Commission and French Research Agency

Juan Rey

CTO, Siemens EDA

Juan Rey

CTO, Siemens EDA

Bio:

Juan C. Rey returned to the Calibre Segment and was appointed as Sr. Vice President, Segment Leader/General Manager for Siemens EDA in April of 2025. Prior to his appointment as GM, Juan led the Central Engineering Solutions Team as part of a government program focused on 3D flows. He Transitioned to Central Engineering Solutions Team after serving as Vice President of Government Programs for Siemens EDA where he was responsible for defining technical programs to support government initiatives since 2023. Prior to his work with Government Programs, Juan held the roll of Vice President of Calibre Engineering. He joined Mentor Graphics in 2001 as Senior Engineering Director for Mentor?s industry-leading Calibre product line, directing all development activities for Calibre products, a role he performed until December 2021. Prior to his time at Mentor Graphics, Juan was Vice President of Engineering at Exend Corporation, managing all software development and quality activities. He joined Extend after serving as Engineering Director of Physical Verification at Cadence Design Systems. Earlier positions include Manager/Developer for Process Modeling and Parasitic Extraction at Technology Modeling Associates, Visiting Scholar/Science and Engineering Associate at Stanford University, Senior Research Engineer at INVAP, Argentina, and Associate Professor at Universidad Nacional del Comahue, Argentina. Juan holds a degree in Nuclear Engineering from Universidad Nacional de Cuyo, Argentina. The author or co-author of numerous papers and conference presentations, he serves on the Executive Technology Advisory Board of Semiconductor Research Corporation (SRC) and the UCLA Center for Domain-Specific Computing.

Stuart Knight

President, HORIBA Group Corporate Officer

Stuart Knight

President, HORIBA Group Corporate Officer

Bio:

Stuart Knight is Materials and Semiconductor Strategy Director and HORIBA Group Corporate Officer, with more than three decades of experience in the global semiconductor industry. He began his career in 1992 in Hong Kong, working for a back‑end semiconductor equipment manufacturer, gaining first‑hand experience of high‑volume manufacturing environments in South East Asia.After returning to Europe in 1998, Stuart joined HORIBA, where he helped establish and grow the company’s semiconductor portfolio, delivering process monitoring and control solutions for semiconductor process optimisation to customers across Europe and globally. He spent many years building HORIBA’s presence in the semiconductor segment before moving into senior executive leadership.

Today, Stuart contributes actively to European and global semiconductor strategy for the HORIBA Group, bringing a practical, manufacturing‑led perspective to industry discussions

Abstract:

The semiconductor industry is increasingly defined by system level complexity, where performance, yield, and sustainability depend on the ability to sense, measure, and control interactions across the entire value chain.

HORIBA addresses this challenge through a woven value chain of sensing and metrology solutions, connecting materials characterization, process monitoring, device performance, and fab and sub fab environments. Built on decades of expertise in analytical instrumentation and supported by a strong global footprint, this integrated approach enables continuous insight from upstream R&D to high volume manufacturing.

By connecting core technologies, product organizations, and global operations, sensing and metrology emerge as a strategic enabler for innovation, yield, and industrial resilience. This integrated approach illustrates how semiconductor leaders can shape scalable growth, accelerate technology adoption, and support a more sustainable semiconductor ecosystem.

Mark Fuselier

SVP, Technology and Product Engineering, AMD

Mark Fuselier

SVP, Technology and Product Engineering, AMD

Bio:

Mark Fuselier is senior vice president of Technology and Product Engineering at AMD. He is responsible for silicon and packaging technology development and new product introduction engineering.

Fuselier has more than 29 years of semiconductor industry experience and has been involved in the development and production of process technology generations spanning from 35 micron through 2 nm across multiple fabs and product families. He played a central role in the development and productization of computing solutions such as 2 nm, multicore CPU and GPU SoC integration, heterogenous APUs, 2.5D and 3D chip packaging and chiplet System in Package (SiP) integration.

Fuselier holds a Master of Science degree in electrical engineering and Master of Business Administration from the University of Texas at Austin. He is a member of IEEE and the Electron Devices Society.

Takahiro Ogura

President of AI Computing Division, Preferred Networks

Takahiro Ogura

President of AI Computing Division, Preferred Networks

Bio:

Takahiro Ogura is a seasoned leader in high-performance computing with over 20 years of experience. He currently heads the AI Computing Division at PFN, overseeing the company's critical computing infrastructure technologies including the MN-Core™ series of AI semiconductors and in-house supercomputers. Prior to joining PFN, he served as the after-sales service manager for domestic high-performance computing clients at Fujitsu, where he began his career as a systems engineer working on supercomputer systems projects. A notable career highlight was his instrumental role in the design and development of the Fugaku (Post-K) supercomputer at Japan's national research and development agency RIKEN. Ogura received a Master's degree from Tsukuba University's Systems and Engineering program in 2005.

Abstract:

As generative AI continues to evolve, the importance of inference computing is poised to grow steadily. In this session, the speaker Takahiro Ogura will introduce the 3D-stacked memory structure, a technological breakthrough for AI inference chips, and demonstrate its potential for social transformation through AI agents and edge AI. Ogura will also share his company Preferred Networks’s vision for democratization of AI and creation of new paradigms through their proprietary chip design, ecosystem development and industry collaborations.

John Neuffer

President & Chief Executive Officer, SIA

John Neuffer

President & Chief Executive Officer, SIA

Bio:

John Neuffer is President and CEO and ex officio board member of the Semiconductor Industry Association (SIA), which has been the voice of the chip industry for nearly five decades. He has been at the nexus of technology, public policy, and trade for most of his career. Since joining SIA in 2015, John has led the association’s policy advocacy in Washington and capitals around the world to foster growth and innovation in semiconductor design, manufacturing, and research.

John also serves as a member of the Board of Directors of the Semiconductor Research Corporation, the world’s leading non-profit industry-government-academia microelectronics research consortium. Additionally, he is a member of the Science & Technology Action Committee and the Council on Foreign Relations.

Prior to joining SIA, John served as Senior Vice President for Global Policy at the Information Technology Industry Council, where he led a global team to expand market access opportunities for member companies around the world. He directed all global government relations in trade, cybersecurity, standards, regulatory, Internet governance, and privacy.

Previously, John served for over seven years at the Office of United States Trade Representative (USTR) in Washington, DC: two years as Deputy Assistant U.S. Trade Representative for Asia-Pacific Economic Cooperation (APEC) Affairs, preceded by over five years as Deputy Assistant U.S. Trade Representative for Japan.

Prior to his tenure with USTR, John was a Senior Research Fellow and Political Analyst with the Mitsui Kaijyo Research Institute in Tokyo for nine years. As a leading commentator on Japanese politics and policy at the institute, he published a widely read newsletter and wrote regular commentary for the Asian Wall Street Journal, TheStreet.com and Newsweek Japan. All told, John lived in Japan 11 years. He is a native of Montana and Washington State.

Michael Schaffert

SVP, Robert Bosch

Michael Schaffert

SVP, Robert Bosch

Bio:

Michael studied electrical engineering at the Technical University of Stuttgart.

In 1998, he joined Bosch in Stuttgart as hardware development engineer for Engine Control Units. 2001, he joined ETAS GmbH in Stuttgart as a Product Manager for Rapid Prototyping system. He left ETAS 2011, when he was Director for Product Management and Development and responsible for all ETAS HW. After ETAS Michael became Vice President at BOSCH and was the Head of Center of Competence for Vehicle Electrics and Electronics Architecture. In this role he was responsible for future E/E-Architecture’s development incl. responsibility for recognizing and assigning new technologies. In 2015 he moved to BOSCH Japan and was the Head of Customer Engineering responsible for Asian Pacific Engine Control Units & SW Service Business. In 2019 he came back to Germany and became Head of HW Development for Powertrain Control Systems BOSCH. In 2020 he was founding member of the new BOSCH Division XC (Cross-Domain Computing Solutions) and had the role as the head of Product Group responsible for Base-SW and Middleware incl. OS Product & Services. Since 07/2022 he joined BOSCH Tier2 as a SCP responsible for Chiplet.

Abstract:

The CHASSIS initiative marks a transformative step in automotive compute platform design for Software-Defined Vehicles (SDVs). By leveraging chiplet-based architectures, CHASSIS addresses the inherent limitations of traditional monolithic System-on-Chips (SoCs), introducing a modular and scalable approach to semiconductor design. This paradigm shift enables tailored, high-performance computing solutions that accelerate the transition to software-defined mobility and foster competitive innovation across the automotive industry.

Our vision extends beyond technical advancement: CHASSIS aims to restore European technological sovereignty in automotive semiconductor innovation through the creation of a multi-vendor chiplet ecosystem. This ecosystem ensures architectural flexibility, automotive-grade reliability, and freedom from proprietary constraints, paving the way for open, future-proof compute platforms.

By delivering scalable architectures that meet diverse performance requirements,